Recently, breakthrough progress has been made in reinforcement design technology of SEU of deep submicron integrated circuit by the programmable chip and system research team headed by Professor Haigang Ynag in our Electron Institute, who proposed a novel three interlocking structure latch (TILL). The test illustrated that the present method was increased by 1 order of magnitude in performance index of anti-single particle and comprehensive “delay-area-soft error rate” compared with that of the traditional double cross lock structure latch (DICE) in more than 20 years. Based on the results, doctoral student Tianwen Li, his mentor Haigang Yang Professor and other 3 research personnel published the paper of “A CMOS Triple Inter-Locked Latch for SEU Insensitivity Design” (Vol.61, No.6, December, 2014) in the Top SCI Journal IEEE Transactions on top Nuclear Science on anti irradiation technology.

When chip is used in space environment, a variety of cosmic rays and particles may hit and pass through circuit, the track of which will have ionization and production of electron-hole pairs. After these electron-hole pairs are absorbed by circuit nodes, timing circuit and memory circuit data errors will be caused, resulting in dysfunction or even lose effectiveness of electronic systems, the effect of which is known as Single Event Upset (SEU). With the decreasing of integrated circuit manufacturing process node, circuit is more susceptible to the influence of space radiation. Flip-latch is a key timing unit in large scale integrated circuits, and particularly it is sensitive to spatial single event effect. Improving its anti-SEU performance is critical to the overall anti-irradiation properties of circuit.

Anti-radiation reinforcement methods can be divided into two kinds: special process method and circuit design method. Reinforcement process is a method using special processing line of chip production and reducing collection of electron-hole pair by devices. However, the production process of special process line is complex, and it is often lagged behind that of the commercial process, but it reduces chip integration. Therefore, realizing anti-radiation method by the circuit design obtains fast development. The current commonly used reinforcement and design methods of latch include three-modular redundancy, Soft Error Masking (SEM), Schmitt Trigger (ST) structure, Dual Inter-locked Cell (DICE) technology et al.. Three-modular redundancy technology eliminates a single flip error by majority decision mechanism, but it does not improve rollover threshold of basic unit, and it increases size and power consumption and reduces speed, which thus limiting its application in large scale integrated circuit. SEM and ST structure was improved based on the ordinary latch, increasing node capacitance and feedback path delay. Although it improves the overturning resisting ability of circuit node, the circuit performance is reduced. When there are overturns in two nodes of DICE structure at the same time turns, there will still be a function of error.

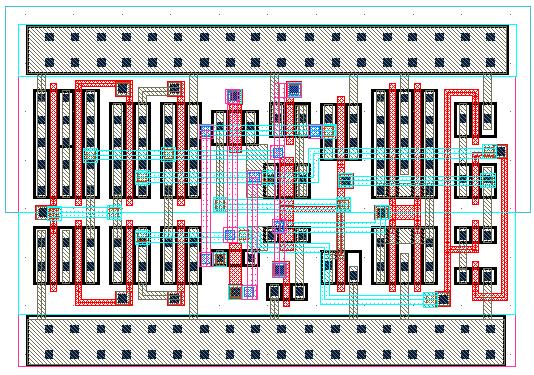

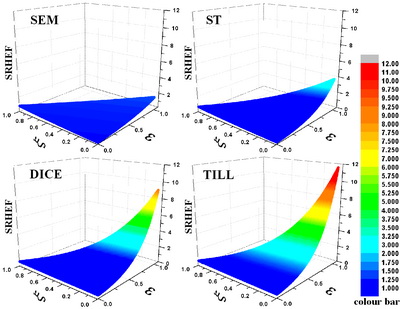

Under the guidance of his mentor, Haigang Yang Professor, doctoral student Tianwen Li developed a novel Triple Inter-Locked Latch (TILL) by long-term in-depth research and constant continuous optimization design of experiment, as shown in Figure 1. Compared with the performances of some other traditional SEU reinforcement latch, the structure circuit is immune to the SEU appeared in multi nodes, of which the speed of three interlocking structure is improved by 24%, power consumption delay is reduced by 22% and area is only increased by 17%. In comparison with the reinforcement efficiency of SEU of other structures, namely soft error rate of module (area* delay consumption power), the comparative analysis shows that the three interlocking structure has the highest efficiency of reinforcement, as depicted in Figure 2.

Figure 1 Three interlocking structure (TILL) reinforcement latch

Figure 2 Comparison of SEU reinforcement efficiency of TILL and the other structures

The test chip is realized by using advanced criteria of the CMOS process design. The single event irradiation test detection system of the chip and the irradiation environment are shown in Figure 3. The comparison results of flip section obtained by irradiation test are demonstrated in Figure 4. The threshold value of SEU of the three interlock reinforcement structure is greater than 42MeV-cm2/mg, and the turning section is at least an order of magnitude lower than that of the traditional reinforcement structure.

At present, the research results have been applied in the latest chip products of the Research Laboratory to further enhance the reliability and anti irradiation ability of space application of domestic "Huixin" series chips. (The Eleventh Section, Zhihong Huang).